meta data for this page

Frequenzteiler 100 MHz

Funktion

Eine Laborreferenz von 100Mhz auf 10MHz runterteilen. Diese 10MHz wird für viele Geräte als externe Referenzfrequenz genuzt.

Ziele

Input: 100MHz +-5dBm Output: 10MHz, 5V TTL und Sinus Ausgang (sinus mit relativ wenig oberwellen)

Status

Fertig. Phasenrauschen noch nicht gemessen. Nachbau moglich.

Entwickler

Thijs Wendrich

Anwender

Das Projekt CASI.

Schaltungsprinzip

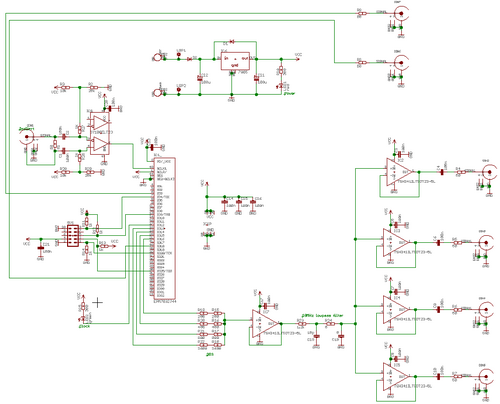

Eingangsstufe: 50 Ohm abgeschlossen, Emitter Coupled Logic (ECL) Teiler: Digitaler Teiler, implementiert in ein CPLD Altera EPM7032SLC (Baureihe MAX7000). Ausgang:

- TTL: via 50 Ohm Wiederstand verbunden mit EPM7032

- Sinus: 4 Bit Analog Ausgang realisiert mit 4 TTL Ausgänge der CPLD und einige Wiederstanden. Anschliesend gibt es ein RC-Filter 2. Ordung. Die Ausgangsstufe ist AC-gekoppelt 50 Ohm

Blink-LED: 0.6 Hz Signal das zeigt das es Funktioniert. Verwendung von der übrige 27 Register der CPLD, da der 100-zu-10 Teiler nur 5 register (16%) braucht.

Schaltplan

- Die Source des Schaltplans ist auf der Download-Seite des Wiki abgelegt. (Direkt-Link: freqdiv.sch)

- Der Schaltplan als png-Graphik :

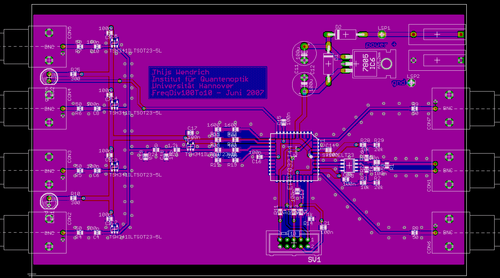

Layout

- Gehäuse:

- Platine größe: 160*100mm

- Versorgung: Einseitig, >7V (alles was eine 7805 glücklich macht), Bananstecker

- Eingang: BNC 50 Ohm abgeschlossen ECL

- Ausgang:

- 2 * BNC 5V TTL

- 4 * BNC Sinus; alle: 50 Ohm

- Anzeigen:

- 1 rote LED für Power

- 1 grüne LED der bei gut funktionieren blinkt.

- Die Source des Layouts im pcb-Format sollten auf der Download-Seite des Wiki liegen, Eagle Board Datei

- Alle Bauteilen sind auf der Oberseite.

Firmware

Chip: EPM7032SLC44-10 Editor/Compiler: Altera Quartus II 7.1 Link zur Quellcode: firmware

- FreqDiv100To10.tdf (Haupt Datei) Text Design File

- DDS10.tdf Text Design File

- MyFreqDiv.tdf Text Design File

- Simulationsdateien: *.vwf

Upload: Altera Byteblaster II auf JTAG Pin verbrauch: 1 input, 7 output Macrocell verbrauch: 31 von 32 (97%) (5 in Statemachine, 24 in ripple divide, 2 unbekant) Beschreibung: Das Program besteht aus 2 Teilen:

- 1 Statemachine, der zähler und sinus umfast.

- 1 ripple divider mit 24 stufen. (Der Compiler find das nicht schon, aber es ist nur für die grüne blink LED).

Bilder

Meckerliste

Was für die nächste Version zu tun ist: (

- EPM7032SLC (5V) ist veraltet und schwer zu bekommen. Ersätzen mit EPM240 (3,3V)

alle Signalpegel nochmals überprüfen.

- Das zusätzliche Phasenrauschen muss noch vermessen werden.